In Compliance with NEP 2020

### Prof. P. NAGABHUSHAN B.E., M.Tech., Ph.D., FIE, FIETE, FIAPS.

Vice Chancellor, VFSTR Life time Professor, IIIT – Allahabad, Prayagraj (Formerly: Director, IIIT-Allahabad 2017-22)

### PREFACE

'You are born to Blossom' – What an inspiring title the book authored by APJ Abdul Kalam and Arun K Tiwari carries. The journey to blossom has got to be heralded by education. The purpose of education is to ensure that the 'Life Blossoms'. Earning a degree and getting a placement should be the just happening things, and should not become the only celebrated goals for education. In the book cited above, Honourable Kalam, Former President of India, underscores that "The scheme of civil society depends on Educating young people to become enlightened citizens and adults who are responsible, thoughtful and enterprising"

VIGNAN aims to seed these concepts in every learner who transits through this temple of learning. The doctrine of VIGNAN entitled R-22 contains the principles of policies laid down by the University, to realize the spirit of "Blossoming the lives" providing a foundation-strong professional education on the ethos of 'Creative learning for Critical thinking and Critically analysing for Creative decision making'. Certainly, our University is one of the earliest Universities, in fact the University is a trend setting one in completely internalising the concepts of the policies brought out in National Education Policy (New Educational Policy) NEP-2020, and inculcating the spirit in R-22. The R-22 document articulates the Academic Regulations of the University, which is being presented now and shall be inforce with immediate effect from the academic year 2022-23, not only for those who have joined in 2022, also the aspirants of 2021-22 are enabled into the navigation.

*R-22* presents a novel design for the academic pursuit, making an exploratory cross disciplinary traversal for a learner who should find learning both holistic and experiential. The learner is ensured to enjoy the continuity in learning and the learner is supported to align and realign, enroute utilising the benefits of constructive feedbacks that s/he receives because of continuous assessment. S/he will be empowered to enjoy the opportunities to explore, experiment and experience.

*R-22* eliminates the melancholy of examinations. The expected severity of breakdown due to the anxiety of examination system is replaced by an affectionate assessment system, increasing the effectiveness in accomplishing the outcomes.

In brief, NEP-2020 compliant revised academic regulation of the University – the R-22, is VIGNAN's commitment to alleviate the acuteness in the present educational practices. It intends to provide a strategic solution to the critical observation made by Bharat ratna awardee, Professor. CNR Rao – "India has exam system, not education system. When will young people stop taking exams and do something worthwhile?" (Thought for the Day, Times of India 13.08.2022)

*Here is R-22, which assures that the learners at VIGNAN are bound to do something worthwhile – very much worthwhile.*

# R22 M.Tech.

# **REGULATIONS - TABLE OF CONTENTS**

|    |        |                                                | Page<br>Numbers |

|----|--------|------------------------------------------------|-----------------|

|    | EXECU  | TIVE ABSTRACT                                  | vii             |

| 1  | INTROE | DUCTION                                        | vii             |

|    | 1.1    | Definition                                     | viii            |

|    | 1.2    | Academic Administration                        | ix              |

|    | 1.3    | Programme Duration                             | ix              |

|    | 1.4    | Courses and Credits                            | ix              |

|    | 1.4.1  | Content and Delivery of a Course               | x               |

|    | 1.5    | M.Tech Degree                                  | x               |

|    | 1.5.1  | M.Tech with Add-on Certification               | x               |

|    | 1.6    | Composition of an Academic year                | x               |

|    | 1.7    | Semester wise provisions                       | xi              |

| 2. | CURRIC | CULUM                                          | xi              |

|    | 2.1    | Distribution of credits                        | xi              |

|    | 2.2    | Organisation of course contents                | xii             |

| 3  | CHOICE | BASED CREDIT SYSTEM                            | xii             |

|    | 3.1    | Professional Core                              | xii             |

|    | 3.2    | Electives                                      | xii             |

|    | 3.3    | Inter disciplinary courses                     | xiii            |

|    | 3.4    | Teaching Assistantship                         | xiii            |

|    | 3.5    | Inter Departmental Project                     | xiii            |

|    | 3.6    | Project                                        | xiii            |

|    | 3.7    | Internship                                     | xiii            |

| 4. | ATTEN  | DANCE                                          | xiv             |

| 5  | ASSES  | SMENT                                          | xiv             |

|    | 5.1    | Marks Distribution                             | xv              |

|    | 5.2    | Qualifying Criteria                            | xv              |

|    | 5.3    | L – based courses integrated with P/T          | xv              |

|    | 5.3.1  | Formative Assessment                           | xv              |

|    | 5.3.2  | Summative Assessment                           | xvii            |

|    | 5.4    | P – based courses                              | xviii           |

|    | 5.4.1  | Formative Assessment                           | xviii           |

|    | 5.4.2  | Summative Assessment                           | xviii           |

|    | 5.5    | Assessment and Grading of MOOCs based elective | xix             |

|    | 5.6    | Inter Departmental Project                     | xix             |

|    | 5.6.1  | Formative Assessment                           | xix             |

|    | 5.6.2  | Summative Assessment                           | xx              |

|    | 5.7    | Project                                        | xx              |

|     |                            | I                                                |        |  |  |  |  |  |

|-----|----------------------------|--------------------------------------------------|--------|--|--|--|--|--|

|     | 5.7.1                      | Formative Assessment                             | xx     |  |  |  |  |  |

|     | 5.7.2                      | Summative Assessment                             | xxi    |  |  |  |  |  |

|     | 5.8                        | Internship                                       |        |  |  |  |  |  |

|     | 5.8.1                      | Formative Assessment                             | xxii   |  |  |  |  |  |

|     | 5.8.2                      | Summative Assessment                             | xxiii  |  |  |  |  |  |

| 6.  | SEMES                      | TER – END ASSESSMENT ACTIVITIES                  | xxiii  |  |  |  |  |  |

| 7.  | COMPU                      | TATION OF GRADING                                | xxiii  |  |  |  |  |  |

| 8.  | SUPPLEMENTARY EXAMINATIONS |                                                  |        |  |  |  |  |  |

| 9.  | GRADE POINT AVERAGE        |                                                  |        |  |  |  |  |  |

|     | 9.1                        | SGPA                                             | xxv    |  |  |  |  |  |

|     | 9.2                        | CGPA                                             | xxv    |  |  |  |  |  |

| 10. | AWARD                      | OF CLASS                                         | xxv    |  |  |  |  |  |

| 11. | AWARD                      | OF DEGREE                                        | xxvi   |  |  |  |  |  |

| 12. | Honora                     | ble exit with Engineering PG Diploma             | xxvi   |  |  |  |  |  |

| 13. | Onward                     | continuation to Ph.D Program                     | xxvi   |  |  |  |  |  |

|     | 14.1                       | Volunteer 'Drop' with Sabbatical Semester option | xxvii  |  |  |  |  |  |

|     | 14.2                       | Volunteer 'Drop' with a semester Drop option     | xxvii  |  |  |  |  |  |

| 14. | INTERP                     | RETATION OF RULES                                | xxvii  |  |  |  |  |  |

|     | Annexu                     | re – 1 Course Structure                          | xxviii |  |  |  |  |  |

R22 M.Tech. YEAR Programme

\* Programme will be offered based on satisfactory strength of students willing to register, after receiving the formal AICTE approval.

# Academic Regulations, Curriculum and Course Contents

### **EXECUTIVE ABSTRACT**

R22 - Academic regulations, Curriculum and course contents, is an articulation of the VFSTR deemed to be University's commitment towards NEP-2020, with a view that it enables student(s) to maintain the spirit of continuous learning and continuous assessment to replace the normal tendency of preparing just before a test or an examination. The proposed framework accomplishes multi-disciplinary holistic education, continuous assessment along with multiple honorable exit options if a student falls short to complete the requirements to earn the degree within the stipulated period including the permissible spill over period.

R22 is oriented towards holistic education at the postgraduate level that includes integrated and rigorous exposure to professional domains, as well as sufficient flexibility in curricular structures that allow students to choose electives from the wide choice of courses. Such holistic and diverse education will assist the candidate in transforming into all-rounded persons. Similarly, in line with NEP-2020, more weight is given to continuous/ formative assessment, in the frame work of an Integrated learning model comprising Learning – Thinking – Understanding – Skilling – Applying – Creating. Emphasis on continuous formative assessment with a creative summative assessment will facilitate the candidate to "Move away from high stake examinations – towards more continuous and comprehensive evaluation".

The M.Tech. degree offered will be for two years' (4 semesters) duration with lateral exit options within this period, with suitable certifications that will enable the candidate to have a professional career and as well as serves as a reminder to return and update his / her qualification in the future. In line with NEP-2020, following one year of study and the completion of the required credits, an Engineering PG Diploma degree will be conferred. However, the intention of the learners is not to join for the award of the PG diploma with lateral exit, but to acquire a M.Tech. degree.

### Salient features of the regulation

- Continuous learning

- Continuous assessment

- Add-on certification

- Honorable exit option

- Onward Continuation to Ph.D. Program

- Sabbatical Semester Drop option to pursue innovation, incubation, entrepreneurial and advanced exploratory activities and subsequent re-entry

### **1** INTRODUCTION

This document contains the academic regulations, scheme of assessments, curriculum, detailed syllabi, course contents with text / reference books recommended, course outcomes, skills acquired and the projects / assignments that are to be performed for each course for the conduct of 2-year M.Tech. degree programmes. The various M.Tech. degree programmes under different schools in VFSTR are as listed below. The character codes indicated in paranthesis are their branch disciplinary code.

### I. School of Agriculture & Food Technology

- Food Processing Technology (FT)

- Farm Machinery (FM)

# R22 M.Tech. YEAR PROGRAMME

### School of Biotechnology & Pharmaceutical Sciences

- Biotechnology (BT)

- III. School of Computing & Informatics

- Computer Science & Engineering (CSE)

### IV. School of Conventional Engineering

- Structural Engineering(SE)

- Machine Design (MD)

- V. School of Electrical, Electronics & Communication Engineering

- Embedded Systems (ES)

- VLSI (VLSI)

- Power Electronics and Drives (PED)

### 1.1 Definition

Ш.

### For the purpose of R22 regulation, definitions as follows shall apply:

- "Degree" shall refer to the M.Tech. Degree Program.

- **"Course**" shall refer to such Course(s) for which a student shall earn Credits after due assessment as per the laid provisions. Project is also treated as a Course.

- "Academic activities" shall refer to the activities like Lecture (Physical Lecture Session), Tutorial (Participatory discussion / Self-Study / Desk Work / Quiz / Seminar Presentation, *etc* activities that make the student absorb & assimilate, the delivered contents effectively) and Practical / Practice sessions (includes Hands on Experience / Lab experiments / Field Studies / Case Studies *etc* activities that enable the student to acquire the requisite skill).

- **"Continuous Assessment"** shall refer to the assessment of the student spread over the entire semester on the various constituent components of the prescribed course.

- "Semester" shall refer to a period covering the two assessment periods *viz* Formative and Summative Assessment period. A semester would generally be spread over twenty weeks.

- "Course Drop" shall refer to a student having to undertake a repeat of the Course(s) not being able to complete the Credit requirements of the Course(s), under the conditions stipulated in the regulation.

- "Supplementary Examinations" shall refer to the examination(s) conducted to allow the student to appear in the un-cleared Semester End summative assessment component.

- "Blank Semester" shall refer to a Semester in which a student either does not register for any course at the beginning of the Semester OR chooses to DROP all courses OR is so compelled to DROP all the courses, as the case may be.

- "Semester Drop" shall refer to availing a blank semester. However, if drop is availed to pursue a creative extension activity, then it is defined as semester sabbatical.

- "Spill Over Semester" shall refer to the additional semester(s) beyond the completion of prescribed normal semesters.

- "AAA Section" shall refer to the Academics, Assessment and Awards Section of the Institute.

- "Attendance" refers to the Physical personal presence in an academic activity session.

- **"Summer Semester"** refers to a Semester that is scheduled to be held during the intervening period of Even and Odd Semester (*i.e.* Summer Vacation period).

- **"Themes"** refer to the courses offered in a particular stream other than offered by the regular departments, for example NCC, Entrepreneurship, Fitness and Living, *etc*.

- **"School"** refers to a division of institute dealing with two or more specific areas of discipline / study comprising of the departments related with exclusive emphasis on trans-disciplinary research.

- "Department" refers to a division of institute dealing with a specific area of discipline / study.

- "HoD" refers to the Head of the respective Department, where the student is enrolled . for his / her Branch of Study.

- "Center" refers to a structured unit within the school / department established with the purpose to carry out advanced research.

- "Grade Point" refers to the quantification of the performance of a candidate in a particular course as defined herein.

- "SGPA" refers to the Semester Grade Point Average and is calculated as detailed in the regulations subsequently.

- "CGPA" refers to the Cumulative Grade Point Average and is calculated as detailed in the regulations subsequently.

- "Division" refers to the Division awarded to the student as per the mechanism detailed in the regulations subsequently.

- "Internship" refers to onsite Practical Training offered by reputed companies / Institutions, in India or abroad. To be undertaken with (or seeking) prior approval of the respective HoD.

- "Project" refers to a course executed by a candidate on a specific research problem at VFSTR / any organization of repute. To be undertaken with (or seeking) prior approval of the respective HoD.

- "Credit equivalence and credit transfer committee" refers to the committee designated to look into for credit equivalence and credit transfer.

- "Honorable Exit Option" refers to the Exit Options available to students, when they are unable to complete the prescribed two-year M.Tech. Degree program in four successive years.

### **Academic Administration** 1.2

The academic programmes of VFSTR are governed by the rules and regulations approved by the Academic Council from time to time. The various academic activities are conducted following a fixed time schedule duly approved by the Academic Council in line with the AICTE / UGC regulations. The academic activities of VFSTR are followed meticulously as specified in the academic calendar as approved by the Academic Council. This academic calendar is shared with all the stake holders well before the beginning of the respective academic year. The curriculum and the course contents of all the programmes are discussed by the respective Board of Studies (BoS), analyzed and recommended for implementation. The Academic Council, being the highest statutory body, chaired by the Vice-Chancellor, meets at least twice or thrice a year and discusses, suggests and approves all the important academic matters related to curriculum and course contents in particular including the recommendations of BoS.

The intended revision in regulations (R22) was in principle accepted and recommended by the Academic Council in its 32nd meeting on 10-12-2022. Subsequently respective Board of Studies brought necessary recommendations accordingly, which were duly placed before the Academic Council in its 33rd meeting on 17-6-2023.

### 1.3 **Program Duration**

For the branch disciplines listed in section (1), the regular courses including theory and practical are offered over a period of two years in four semesters. The normal duration to complete the M.Tech. program is two years. However, a student can avail the benefit of spill over period for 2 years, that is the maximum duration of four years can be availed by a candidate to complete the M.Tech. programme in a slower pace if he / she desires. The candidate failing to complete the requirements will be considered for the honorable exit as applicable

### 14 **Courses and Credits**

VFSTR

The term course is used in a broader sense to refer to so called papers such as 'theory subject', 'laboratory', 'inter-departmental project', 'major-project' etc. A course can be of theoretical and / or of practical nature, and certain number of credits are allotted to it depending on the

number of hours of instruction per semester. For a course offered in a semester, one hour of lecture (L) instructions carried out in a week is considered equivalent to one credit, whereas two hours of practical (P) sessions done in a week are considered equivalent to one credit. Depending on the course two hours of tutorial (T) sessions may be considered equivalent to one credit. A student earns these credits when he / she successfully completes the course.

### 1.4.1 Content Delivery of a Course

Content delivery of a Course in the M.Tech. Degree Program shall be through, either or all, of the following methods:

- i. Lecture refers to Lecture Session(s) through classroom contact session wherein students will learn by listening. Denoted by "L".

- ii. Tutorial refers to transaction(s) consisting of Participatory discussion / Self-study / Desk work / Brief presentations by students along with such other novel methods that enable a student to efficiently & effectively absorb and assimilate the contents delivered in the lecture sessions. Denoted by "T".

- iii. Practice refers to Practice / Practical sessions and it consists of Hands-on-Experience / Laboratory Experiments / Field Studies / Case Studies / Minor / Major Project, that equip the students to acquire the much required skill component. Denoted by "P".

### 1.5 M.Tech. Degree

All students formally and conventionally enroll for M.Tech. degree programme. They have to earn **68** credits for the award of degree as specified in the Curriculum. However, additionally he/she can opt to earn up to 12 more credits as Add-on credits, to earn the academic benefits as specified below.

### 1.5.1 M.Tech. with Add-on Certification

If a candidate earns add-on 12 credits in the respective discipline, then he/ she will be eligible for the award of M.Tech. in YY Engineering with Add-on Certification.

**Note:** The consolidated transcript will contain the credits and grade details of all courses amounting to 68 + up to 12 credits.

### 1.6 Composition of an Academic year

An academic year is composed of an Odd semester (20 - 22 weeks), an Even semester (20 - 22 weeks) and a Summer semester (6 - 8 weeks). The regular semester that begins in July / August is known as odd / first semester and the one that begins in December / January is known as even / second semester (Figure 1). The instructional days for a regular semester shall be a minimum of 90 working days exclusive of days earmarked for summative assessment.

|               | YEAR OF 12 MONTHS |                |               |               |               |               |               |               |              |              |               |

|---------------|-------------------|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------|

| 1             | 2                 | 3              | 4             | 5             | 6             | 7             | 8             | 9             | 10           | 11           | 12            |

| July/<br>Aug. | Aug./<br>Sept.    | Sept./<br>Oct. | Oct./<br>Nov. | Nov./<br>Dec. | Dec./<br>Jan. | Jan./<br>Feb. | Feb./<br>Mar. | Mar./<br>Apr. | Apr./<br>May | May/<br>June | June/<br>July |

|               | ODD SI            | EM/ FIR        | ST SEM        |               | E             | VEN SE        | M/ SEC        | OND SE        | М            | SUM<br>SE    |               |

Figure 1: Distribution of semesters during an Academic Year.

**1.6.1** Before the commencement of the semester, a candidate has to pay the stipulated tuition fee and submit an application detailing the courses he / she intended to register, valid for that respective Odd / Even semester. The maximum number of credits per semester will be 25 credits inclusive add-on credits. The intended semester wise coverage will be as presented in the curriculum.

- **1.6.2** Summer semester is a short duration semester program that will be generally conducted during the semester break between even semester and odd semester. The students having 'R' (Repeat grade) courses may register for the course work during this semester to get a chance for successfully completing the 'R' courses. In general, supplementary assessments are conducted in the later part of the summer semester. However, the courses offered in summer semester and the number of courses a student can register are subjected to academic and administrative convenience. A student may register up to a max. of 12 credits in a summer semester.

- 1.6.3 Exception to the routine practice of registering for 'R' courses in summer semester, a student can register in a course offered by a visiting expert during the summer vacation which may be equivalent to a department elective or an Add-on-course. The candidates can register for such courses within the scope of 12 credits. Candidate may also avail summer semester for summer internship opportunities, which may be considered as Add-on credits.

### 1.7 Semester wise provisions

A student may register for a max of 25 credits per semester as prescribed or otherwise he/ she may include the Repeat courses in the event of having not successfully completed a course or courses in the earlier semester. However, a student may also opt to go in a slower pace to earn the credits less than the prescribed max of 25, including even 'Dropping' a semester for special reasons.

It should be clearly underscored that a candidate should on priority register for Repeat (R) credits if any, during a regular semester, within the said scope of 25 credits; in case he / she cannot be sure of completing or could not complete the 'R' credits in Summer semester.

- 1.7.1 During the first two years from the date of admission to M.Tech., a candidate has to pay the semester / annual fees as prescribed irrespective of the less number of credits that he / she would register or even opt to Drop a semester.

- **1.7.2** If a candidate gets into spillover semester beyond two years up to a maximum of four years he / she has to pay semester fee proportional to the credits that he/ she registered in that spill over semester as prescribed from time to time.

- **1.7.3** A candidate has to pay additional fee proportional to the number of credits for registering in a summer semester as prescribed from time to time.

### 2. CURRICULUM

Each School offers different M. Tech. degree programmes and the departments concerned prescribes semester-wise curriculum encompassing different courses. Every course offered will be designated in a L-T-P structure. The theory courses comprise of L (and / or T & P hours) whereas the practical courses include instructions (T) and practical sessions (P). Amalgamation of theory courses with practical sessions is predominantly seen in this curriculum.

### 2.1 Distribution of credits

The overall distribution of credits for various categories of courses in the curriculum of M.Tech. programmes is represented in Table (1) as given below.

Table 1 : Credits Distribution for Various categories of courses.

| Category of Courses        | Credits (%) | AICTE<br>Recommendation (%) |

|----------------------------|-------------|-----------------------------|

| Professional Core          | 29.4        | 29.4                        |

| Electives                  | 17.6        | 22.1                        |

| Inter disciplinary courses | 8.8         | 7.4                         |

| Projects                   | 44.1        | 41.2                        |

### 2.2 Organization of course contents

Courses offered in the program is composed of two modules covering all the course contents required for a candidate to obtain knowledge and skill. Content in each module is further distributed among two units; wherein Unit -1 contains 'Fundamentals and Broad perceptive' of the module. Unit-2 comprises of the extension / advanced topics of Unit-1 as well as necessary practice models for validation / applying the knowledge gained during L/T sessions. The modular period is about 8 weeks. The first unit in a module may be covered in 2 to 3 weeks and the second unit of the module maybe of 5 to 6 weeks (Figure 2). By the end of each module a candidate must be in a position to translate his/ her L-based knowledge into P-based skill as prescribed in the curriculum. Individual formative assessment shall be in place for each module and a single semester-end summative assessment for the course composed of both the modules.

|                               | YEAR OF 12 MONTHS |                |               |               |               |               |               |               |              |              |               |

|-------------------------------|-------------------|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------|

| 1                             | 2                 | 3              | 4             | 5             | 6             | 7             | 8             | 9             | 10           | 11           | 12            |

| July/<br>Aug.                 | Aug./<br>Sept.    | Sept./<br>Oct. | Oct./<br>Nov. | Nov./<br>Dec. | Dec./<br>Jan. | Jan./<br>Feb. | Feb./<br>Mar. | Mar./<br>Apr. | Apr./<br>May | May/<br>June | June/<br>July |

|                               | ODD SI            | EM/ FIR        | ST SEM        |               | E             | EVEN SE       | M/ SEC        | OND SEI       | N            | SUM<br>SE    | MER<br>M      |

| Module- I Module- I Module- I |                   |                |               |               |               |               |               |               |              |              |               |

| U1                            | U2                | U1             | U2            |               | U1            | U2            | U1            | U2            |              |              |               |

Figure 2: Unit-wise distribution of course contents in a module and their mapping with Academic Calendar; U= Unit.

### 3. CHOICE BASED CREDIT SYSTEM

Each branch discipline of the M.Tech. programme comprises of a set of courses - professional core, electives, projects and audit courses. VFSTR offers flexibility for students to choose courses of their choice and obtain the credits satisfying the minimum credits criterion in each category as given in Table-1.

### 3.1 Professional Core

Professional Core courses are individualized for each programme and they are mandatory for every student opting for that branch discipline. These are designed to offer the essential fundamental knowledge and skills required for that specific programme.

### 3.2 Electives

A candidate has a choice to choose the elective courses. A list of elective courses are pooled together, enabling a candidate to choose the electives from a pool. There may be more than one pool in certain disciplines aligned to a specific theme. Otherwise also he/ she can exercise the choice to choose electives from across the pools. There may be courses which may not be listed under any pool, which are called 'Free elective courses'.

Elective courses offered for each programme are categorized as 'program electives' that are aimed at offering the advanced/ additional knowledge in the chosen branch discipline.

Care should be exercised while opting for program elective courses and Add-on certification courses that is a course opted as program elective should not be registered as a course under Add-on certification courses and vice versa.

Apart from 68 credits, additionally candidate has to earn 12 credits for Add-on certification. Of these 8 credits may be earned through MOOCs offered via Swayam platform. A student may also be permitted to earn more elective credits through MOOCS. This will promote self-learning and drive students towards innovative learning approaches.

To facilitate the process of acquiring the elective credits through MOOCS, VFSTR has constituted "Online course committee" at Central level with 1-2 members represented from each of the department to guide students in selection of courses and to assist them with further steps if required until completion of the courses.

### 3.3 Inter disciplinary courses

Courses such as Cyber security, Research Methodology & IPR and employment Orientation/ Soft skills program are offered in the first and second semester of the programme. As per UGC guidelines cyber security course is introduced as compulsory course. The M.Tech. students are encouraged to participate in research activity of both academia and industry, hence research methodology & IPR could be an important course to offer.

The 50-hour Employment Orientation Program (EOP) for M.Tech degree students is conducted with the help of in-house and invited experts. It is aimed at improving presentation skills in general and pedagogical skills in particular.

### 3.4 Teaching Assistantship

Candidates after undergoing Employment Orientation Programme in the first semester of the program should enroll for the 'Teaching assistantship' course during their second semester to earn 2 credits. Each candidate will assist faculty in handling a 'P-based activities' for B.Tech. students, developing teaching abilities like handling the sessions, interaction with students for clarification of doubts and assessment capabilities. The candidate performance will be assessed in the same lines.

### 3.5 Inter Departmental Project

These projects are designed and executed by students during the first year second semester of their program. By doing these projects, students will get an idea of how technologies or processes, prototype or working model can be developed by culmination of technologies from courses of different programs. The minimum duration of inter-departmental project during each of the semester is 90 hours including writing of project report and submission for assessment. A batch of 2-3 students from same or across the departments can take part in each of the inter-departmental projects. Performance will also be assessed in the modular framework for formative and semester-end summative with a weightage of 2 credits

### 3.6 Project

Students may opt for Project work in lieu of internship for two complete semesters during second year. Such students may avail research-internship support from any institution well known for research and development (R&D). They may also take up project work in VFSTR itself. Each candidate has to submit interim reports and a final report which are mandatory requirements towards the partial fulfillment of project credits requirements. It bears a weightage of 13 credits for the work executed in the third and fourth semesters totalling up to 26 credits. During the project work the student under the guidance of a faculty member(s) will involve in an innovative design / research through the application of his / her knowledge gained in various courses studied. He / she is therefore expected to present a survey of literature on the topic, work out a project plan and carry it out through experimentation / modelling / simulation / computation. Through such a project work, the student is expected to demonstrate system analysis, design, presentation and execution skills. Performance in the project will also be assessed in the modular framework for formative and summative assessments.

### 3.7 Internship

A student can undertake internship in lieu of project work in industry for two complete semesters during second year in lieu of major project work. It bears a weightage of 13 credits for the work executed in the third and fourth semesters totalling up to 26 credits. This is aimed at training students in solving / understanding real-life problems through application of engineering analysis, design, evaluation and creation, particularly in association with practitioners and experts in the industry. The procedures for obtaining the internship placements and allocation of the same to the students are as per University. Even during internship, a student is preferably expected to carry out a focused study on one topic / problem in consultation with the interning institute. Internship progress report should be submitted periodically and finally a detailed internship report should be submitted duly certified by a mentor from the internship institute. Performance in the internship will also be assessed in the modular framework for formative and summative assessments.

### 4. ATTENDANCE

It is mandatory for the student to attend the course work in each semester as per the academic schedule of that semester. VFSTR expects 100% attendance. However, the attendance in each course shall not be less than 75 % of the aggregate of all L, T, P sessions conducted in that course.

- a) The attendance calculations will be periodically reviewed at the end of every 4 weeks. The details of attendance status will be shared with the parents / guardian. The final status of attendance will be reported at end of 15th week granting the advantage of the attendance for the 16th week for the purpose of attendance shortage calculations.

- b) The shortage of attendance may be condoned up to 10% on the ground of ill-health, social obligations, participating / representing in sports/cultural events, placement activities etc.

- c) Documentary evidence like medical reports and certificates issued by concerned bodies is to be produced on time as support for the attendance shortage due to ill-health. These cases are subjected to the scrutiny of a committee constituted for this purpose by the Vice-Chancellor. The decision of the committee shall be final.

- d) Prior approval has to be taken from the HoDs for the other types of leaves.

- e) The courses where the student shortage of attendance was not condoned shall be considered as 'Repeat' category courses and will be under 'R' grade in the student's semester transcript. Student should re-register for these courses during the summer semester or whenever the course is offered next time during regular semesters. These re-registrations are subjected to the regulations at the time of re-registration. In case of core courses, the same core has got to be re-registered. However, in case of an elective a candidate may exercise a choice of choosing different elective in place of 'R' graded elective.

The students who are put into 'R' grade will not be allowed to take up the summative assessment in that semester. In case due to lack and/or delay in information, if he/she appears for the summative assessment in that course, office of AAA is empowered to cancel the attended exams. The scores obtained either in formative or summative assessment will not be considered for grading.

### 5. ASSESSMENT

Teaching-Learning and Assessment should go hand in hand and complement each other. Continuous assessment plays a vital role to enable the student to get synchronized with the teaching-learning process. Assessment mechanism adopted in the institute is aimed at testing the learning outcomes in tune with the outcome based model of education. The focus, is thus on assessing whether the outcomes are realized by the end of the course.

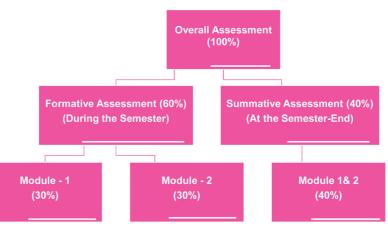

The performance of a student in each course is assessed on a continuous basis during the semester through various in-semester and end-semester assessment models. The marks awarded through continuous assessment are referred to as Formative assessment marks. The marks awarded through end-semester tests are referred to as Summative assessment marks (Figure 3). Both the formative and summative assessment marks are considered for awarding the final marks and the grade point in a particular course.

Figure 3: Categories of assessments in place for R22.

### 5.1 Marks distribution

For each course, the maximum sum of formative and summative assessment marks put together is 100, in the ratio of 60:40, respectively.

### 5.2 Qualifying criteria

To be declared successful in a course, a student must secure at least a grade 4.5 in a scale of 10 based on the total maximum marks which is inclusive of formative and summative assessment. The students should also get 40% from the maximum marks allotted for formative and summative assessments individually.

The hierarchy of qualifying criteria is as follows:

- i. Attendance compliance should be 75% or within condonable range; else the candidate is put into 'R' grade.

- ii. In formative assessment, a candidate should secure a minimum of 40% i.e. 24 marks out of 60; else the candidate is put into 'R' grade.

- iii. In summative assessment, a candidate should secure a minimum of 40% i.e. 16 marks out of 40; else the candidate is put into 'l' (Incomplete) grade.

- iv. Collectively the candidate should secure a min. grade of 4.5 in a scale of 10 after relative grading; else the candidate has to choose either 'R' or 'l' grade duly being counselled.

- v. Every semester, candidate should score a min. of 5 Semester Grade Point Average (SGPA) in every semester individually with the successfully completed courses. In case a candidate fails to score the min. SGPA, then he / she shall voluntarily drop a few Courses to ensure a SGPA of 5. He / she after duly counselled has to choose either 'R' or 'I' grade for the dropped courses.

The candidates with 'R' grade should re-register for 'R' courses either in Summer semester or in a regular semester as and when the courses are offered. The candidates in 'l' grade are allowed to appear for supplementary summative assessment whenever the semester-end assessments are conducted.

To assess special projects / courses, not fitting into the categories described here, a suitable assessment procedure will be evolved in consultation with experts of that area and adjudicated by the committee constituted for that purpose. The decision given by the committee will be final. The appended assessment scheme shall be announced by the course coordinator during the commencement of course.

|               | YEAR OF 12 MONTHS    |                |               |               |               |               |               |               |              |              |               |

|---------------|----------------------|----------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------|

| 1             | 2                    | 3              | 4             | 5             | 6             | 7             | 8             | 9             | 10           | 11           | 12            |

| July/<br>Aug. | Aug./<br>Sept.       | Sept./<br>Oct. | Oct./<br>Nov. | Nov./<br>Dec. | Dec./<br>Jan. | Jan./<br>Feb. | Feb./<br>Mar. | Mar./<br>Apr. | Apr./<br>May | May/<br>June | June/<br>July |

|               | ODD SI               | EM/ FIR        | ST SEM        |               | E             | VEN SE        | M/ SEC        | OND SEI       | M            | SUM<br>SE    |               |

| Mod           | Module- I Module- II |                |               |               | Mod           | ule- I        | Mod           | ule- II       |              |              |               |

| U1 U2 U1 U2   |                      |                |               | U1            | U2            | U1            | U2            |               |              |              |               |

| Fo            | Formative Assessment |                |               |               | Fo            | rmative /     | Assessm       | nent          | SA           |              |               |

**Figure 4:** Schedules of formative and summative assessments in line with Academic calendar. SA = Summative assessment.

### 5.3 L-based courses integrated with P/T

### 5.3.1 Formative Assessment

The scheme of formative assessment is designed to promote the continuous learning. Scheme consists of assessments planned at institute level and assessment that may be scheduled by

the course instructor (Figure 4). Institute level assessments shall be scheduled by the office of AAA. Respective Faculty Member(s) shall declare the schedule of Continuous Laboratory Assessments (CLA), Quiz, Tutorials, Assignments, Seminars, Discussions, etc. Some of the components may also however take place in an unscheduled manner like Surprise Tests. However, students shall be made aware of the assessment modalities that are going to be followed in a course by the faculty, under information to the HoD.

To monitor the progress of students, continuous assessment comprising of five targets (T1, T2, T3, T4 and T5) is advocated in each module for a maximum of 60 marks. For a class, formative assessment commences by the announcement of module bank containing 10 problems for each module in a course. Nature of problems in the module bank shall be at the level of creative / exploratory / design / thought provoking covering the complete syllabus of a module at advanced / challenging level.

The purpose of creating module bank of 10 problems is to assign one problem to each student or to a batches of 2 members. The batches are composed of randomly picked up candidates. These batches remain same for all courses and also for the P-sessions in the courses in that semester and are created in the beginning of that semester.

The purpose of assigning one problem to two batches is to create a healthy competitive spirit between the two batches.

The modality of evaluation of five targets is listed here under:

a) T1: During 5th or 6th week of each module a classroom test shall be conducted. T1 consists of two parts: A and B.

Part A consists of one random problem from the module bank and varies from batch to batch. All the questions in the module bank shall be distributed among students and students shall know the question to be answered only on the day of test in the examination hall.

Part B consists of one common problem at fairly application/ advanced level (not at all prior notified) from outside the module bank for all the students.

T1 shall be paper based and proctored test for a period of 60 min (maximum) which shall be assessed for 30 marks and downscaled to 10 marks.

For the students who for justifiable reasons could not attend the classroom test on the scheduled day, a re-test maybe conducted. However, Part-B will contain a new question and Part-B will have higher weightage than part-A or full weightage could even be allotted for Part-B in such an event

b) T2: Immediately follows T1. Students in a specified batch who now have received the same question during T1 will work further on that problem for T2.

T2 is primarily an extension of problem received in T1 for carrying out validation study: Case studies / Simulations / Experimentation. Each batch shall interact with the course instructor to finalize the nature of validation and expected to complete the exercise within 10 to 15 days after T1.

Course instructor should ensure assigning a different case study / a different scope for validation study for each batch in case the same problem is assigned to two batches.

Course instructor shall assess every student in a batch for a max. of 10 marks based on his observation, interaction and/or reviewing (based on at least two reviews).

c) T3: T3 shall be conducted during the last week of each module. Student batches are expected to submit a report, clearly documenting the work executed during T2. The report should be in IEEE / APA format and additionally a voice in-built PPT should be prepared and submitted.

The report and presentation shall be assessed by the course instructor for 10 marks for every student. In certain cases, a course instructor can call a batch for a physical presentation also.

d) T4: T4 is a comprehensive module test, conducted for 30 min. comprising of 20 multiple choice questions (MCQs) covering the holistic content of module. T4 shall be evaluated for a max. of 10 marks @ ½ mark for each question. T4 will be conducted in ON-LINE mode.

There shall be two tests in each course in a day and the best performance of the tests shall be considered for awarding the marks.

Two sets of question papers each containing 20 questions should be set. The theme of the questions could be similar across the sets. When the test is administered online, every student receives the questions in shuffled sequence and also the choices in shuffled sequence. Therefore, the choice like both 'a' & 'b' above, neither 'a' nor 'b', all the three a, b, c will not be set.

e) T5: T5 assessment is based on Practice or Tutorial assignments. Implementation, Report presentation and Discussion shall happen in a continuous mode throughout the module period.

At least 4 such continuous lab practice assessments (CLPA) / assignments per module shall be conducted by course instructor. The marks will be @ 5 marks per assignment totalling up to 20 per module.

- **f)** The scores of the targets are to be normally announced within three working days on completion of the assessment and the performance is to be discussed in the class.

- **g)** The total marks per module is 60 T1 (out of 10), T2 (out of 10), T3 (out of 10), T4 (out of 10) and T5 (out of 20).

- h) Total marks for both the modules from formative assessment will be added up to 120, which will be *suitably mapped down* to a max. of 60 marks. The mapping policy should be decided by the lead instructor / instructors in consultation with the HoD. The mapping policy should be shared with Dean AAA for the purpose of documentation.

- i) The marks scored in Module-1 for a max. of 60 should be entered / submitted latest by 9th week and of Module-2 latest by 17th week of the semester. Consolidated score for a max. of 120 *suitably mapped down* to a max. of 60 marks should be submitted latest by 18th week of semester enabling the declaration of 'R'- grade before the commencement of summative assessment.

- j) A candidate put under 'R'- grade will not be permitted to take up the summative assessment.

### 5.3.2 Summative Assessment

- a) An instructor may choose one of the two formats for conducting summative assessment for L-based courses integrated with T/P.

- i) 15 + 25 marks format or 20 + 20 marks format (following b, c, d below).

- ii) 40 marks format (following c, d below).

- b) If summative assessment is in two parts format:

- Part-I will be the assessment of capstone project which is pre-assigned during the module-2 period or will be the exploratory review assessment of all lab practice assignments.

- ii) Part-II will be based on a written examination for a max. marks of 80, as in c & d below, which is *scaled down* to 25 or 20 based on the selected pattern of format.

- iii) A candidate should attend both the parts of summative assessments; else he will be put into 'l' grade.

- c) For each L-based course integrated with T/P, the summative assessment shall be conducted by the Institute for a duration of 150 min. and for a maximum of 80 marks. Contents for summative assessment shall cover the breadth and depth of the complete syllabus that is mentioned in the two modules of a course.

d) The question paper for end-semester theory examination consists of two parts as given in Table (2).

Table 2: L-based Summative Assessment Question Paper Pattern.

| Part No. | No. of Questions | Marks for each Question | Marks | Choice |

|----------|------------------|-------------------------|-------|--------|

| А        | 4                | 10                      | 40    | No     |

| В        | 2                | 20                      | 40    | No     |

|          | Total Ma         | rks                     | 80    |        |

- e) The questions will be comprehensive covering the entire course syllabus and any single question should not necessarily be limited to any particular unit / module.

- f) These marks are *suitably mapped down* to a score of 40.

- g) Total marks of summative assessment will be for a max. of 40 irrespective of format of evaluation.

- h) The award of 'I' grade is solely based on marks scored in summative assessment out of 40, if he/she does not score a min. 16 out of 40 (40%).

### 5.4 P-based Courses

The detailed information consisting of experiments, batch formations, experiment schedules, etc., will be displayed / informed to the student in the first week of the semester so that the student comes prepared for the lab sessions. Copies of the manual will be made available to the students along with the schedule. The manual will consist of the list of equipments, detailed procedure to conduct the experiment, format for record writing, outcomes for each experiment and possible set of short questions to help students gain critical understanding. The courses like Cyber security, Research Methodology & IPR will also be treated as P-based courses.

### 5.4.1 Formative Assessment

During practice sessions, a brief viva-voce is conducted for each student on the experiment he/she is carrying out on that day. Some of the parameters that could be included in the Continuous Practice Assessment (CPA) are given in Table (3). The set of parameters may slightly differ from one laboratory to the other, and will be announced before the commencement of the practice session. These parameters are assessed for each laboratory session.

Table 3: Suggested parameters for Continuous Practice Assessment (CPA).

| S. No | Component                                                                                                    | Marks |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

| 1     | Report of about 1 page on proposed experimental layout and background theory before the start of lab session | 4     |  |  |  |  |

| 2     | 2 Viva and interaction to evaluate understanding of concepts                                                 |       |  |  |  |  |

| 3     | 3 Experimentation and data collection                                                                        |       |  |  |  |  |

| 4     | Analysis of experimental data and interpretation                                                             | 4     |  |  |  |  |

| 5     | Finalized report submitted in the next week                                                                  | 4     |  |  |  |  |

|       | Total                                                                                                        | 20    |  |  |  |  |

This assessment is carried out for each practical session and the total marks of all practical sessions will be *suitably mapped down* to a max. of 60.

### 5.4.2 Summative Assessment

End semester examination for each practical course is conducted jointly by two examiners. The examiners are appointed by Dean, AAA from the panel of examiners suggested by the respective Heads of the Department. In some cases, one of the examiner may be from outside the institution and will be identified as external examiner. The scheme of assessment may vary depending on the nature of laboratory, which shall be shared with student by the

laboratory in-charge. The summative assessment will be conducted for a max. marks of 40. The general scheme of assessment is given in Table (4).

### Table 4: Suggested end-semester summative assessment pattern for P-based courses.

| <b>0</b>                                          |            | Marks      |       |

|---------------------------------------------------|------------|------------|-------|

| Component                                         | Examiner 1 | Examiner 2 | Total |

| Objective & Procedure write up including outcomes | 4          | 4          | 08    |

| Experimentation and data collection               | 4          | 4          | 08    |

| Computation of results                            | 4          | 4          | 08    |

| Analysis of results and Interpretation            | 4          | 4          | 08    |

| Viva Voce                                         | 0          | 8          | 08    |

| Total Marks                                       | 16         | 24         | 40    |

### 5.5 Assessment and Grading of MOOCs based elective

Whenever a candidate opts for a course through MOOCS offered via Swayam platform, he / she has to learn and undergo assessment as per norms set by VFSTR for such MOOCs Courses. Upon the declaration of the result, that the candidate has successfully completed the course, the candidate is said to have earned the credits under credit equivalence and credit transfer.

### 5.6 Inter Departmental Project

Inter departmental project work is undertaken in the 2nd semester for earning 2 credits by each candidate. It is expected that the inter- departmental Projects result in publication of a technical paper in a peer-reviewed journal. For this purpose, Dean R&D and Heads of Department will identify faculty mentors who will guide the students by conducting workshops on drafting of research article, communication, process of peer-review, publication, etc. The faculty will support the students by all means to get the technical findings published in peer-reviewed journals.

### 5.6.1 Formative Assessment

The assessment will be carried in two reviews in a systematic way. The detailed assessment guidelines and scheme are to be announced along with the assessment schedule as mentioned in the Table (5).

| No of<br>Module | Schedule              | No of<br>reviews | Points to be considered                                                                                                                                                                                                                                                                                             | Formative<br>assessment<br>marks |

|-----------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Module -1       | 7th – 8th<br>week     | Review -1        | <ul> <li>Identification of specific area out of broad areas under the supervisor</li> <li>Identification of outcomes in line with programme objectives.</li> <li>Feasibility of contributing to the attainment of outcomes</li> <li>Identification of tools / equipment / surveys / training needs / etc</li> </ul> | 30                               |

| Module – 2      | 15th–<br>16th<br>week | Review -2        | <ul> <li>Presentation of results, analysis and conclusions</li> <li>Meeting of objectives defined in first review</li> <li>Preparation of report</li> <li>Understanding by individual students on the overall project</li> <li>Submission of technical article</li> </ul>                                           | 30                               |

Table 5: Schedule and parameters followed for formative assessment.

**R22** M.Tech.

YFAR

ROGRAMME

### 5.6.2 Summative Assessment

Summative assessment will be done jointly by two examiners. The examiners are appointed by Dean, AAA from the panel of examiners suggested by the respective Head of the Departments. In some cases, one of the examiner may be from outside the institution and will be identified as external examiner. The scheme of assessment will be report (15 marks), presentation (10 marks) and demonstration (15 marks) respectively. Points to be considered during the review.

- a) Presentation of results, analysis and conclusions

- b) Meeting of objectives defined in first review

- c) Preparation of report

- d) Understanding by individual students on the overall project

- e) Individual student contribution

- f) Progress of project as per schedule

- g) Submission of technical article/ prototype realization

### 5.7 Project

Those students who do not opt for the internship, carry out their major project at VFSTR and submit their report which is a mandatory requirement for the award of degree. These projects are usually done individually during third and fourth semesters, under the guidance of a faculty member. Every candidate, in consultation with the guide, should define the project and also the probable procedure of carrying it out and submit the same to a committee consisting of 2 to 3 faculty members appointed by Head of the Department. This is to avoid the repetition and also to come up with a roadmap for completion of the project within the time stipulated. The students are encouraged to select topics related to ongoing research and consultancy projects. The students are expected to carry out and present a survey of literature on the topic, work out a project plan and its implementation through experimentation / modelling / simulation / computation. They are also expected to exhibit system analysis, design, and presentation and evaluation skills.

### 5.7.1 Formative Assessment

The progress of project is reviewed twice in a semester by the Project Review Committee (PRC) and formative assessment marks are awarded based on these reviews. The Project review committee consists of

- a) Head of Department or his/her nominee Chairperson

- b) A senior faculty member identified by the HoD member

- c) Project supervisor member

Review schedules of PRC are to be announced by the department immediately after the commencement of semester. The review presentations are open to all the students of that section and attendance is compulsory. The first review should be of 15 minutes / student; second review should be around 30 minutes / student. Before every review every student should submit their PPT along with a brief report of not exceeding two pages. It is to be expected by the committee that student communicates / publishes research article based on the project work prior to graduation either in a peer-reviewed journal or top-notch conference. Based on the recommendations of the committee, he / she is expected to continue same research problem in the third and fourth semesters to derive possible solutions. The following aspects may be considered by the committee for assessment Table (6).

| Table 6: Schedule and | suggested   | parameters t | to be o | considered  | for | formative a | assessment.    |

|-----------------------|-------------|--------------|---------|-------------|-----|-------------|----------------|

|                       | i ouggoolou | paramotoro   | 0 00 0  | oonoraoroa. | 101 | ionnauvo (  | abbobbinionit. |

| Semester        | Module    | Schedule               | Review           | Points to be considered                                                                                                                                                                                                                                                                                       | Max. Marks |

|-----------------|-----------|------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Semester<br>III | Module -1 | 7th – 8th<br>Week      | First<br>review  | <ul> <li>Identification of specific area out of broad areas.</li> <li>Identification of outcomes in line with programme objectives</li> <li>Feasibility of contributing to the attainment of outcomes</li> </ul>                                                                                              | 20         |

|                 | Module -2 | 15th<br>– 16th<br>Week | Second<br>review | <ul> <li>Identification of tools / equipment / training needs / etc.</li> <li>Understanding by individual students on the overall aspect of the project</li> <li>Completion of literature survey</li> <li>Design of project set up</li> </ul>                                                                 | 40         |

|                 | Module -1 | 7th – 8th<br>Week      | First<br>review  | <ul> <li>Acquisition / learning of the tool required</li> <li>Readiness of the layout of the project report</li> <li>Progress review as per mechanism / schedule identified</li> <li>Preparation of draft manuscript for publication</li> </ul>                                                               | 20         |

| Semester<br>IV  | Module -2 | 15th<br>– 16th<br>Week | Second<br>review | <ul> <li>Presentation of results and conclusions</li> <li>Meeting of objectives defined in first review</li> <li>Submission of draft report</li> <li>Understanding by individual students on the overall project</li> <li>Progress of project as per schedule</li> <li>Progress of the publication</li> </ul> | 40         |

### 5.7.2 Summative Assessment

At the end of III & IV semesters, summative assessment of the project will be conducted in two phases.

Phase–I: This is an evaluation for a max of 20 marks. A committee of two members comprising of HoD's nominee and Guide will assess the project work which will involve going through the project report (6 marks), project presentation (7 marks) and demonstration of the project (7 marks).

Phase–II: A final presentation and defense assessment for a max. of 20 marks will be carried out by one-man committee composed of an external expert who is chosen by the Dean AAA from a panel of examiners suggested by the HoD. The format for evaluation will involve going through the project report's quality (6 marks), presentation (6 marks) and interaction and defense (8 marks).

The qualifying marks will be finalized considering the marks scored in both the phases (I & II) of summative assessment.

Publication in a top-notch conference / peer-reviewed journal is mandatory for evaluating the project for 100% weightage.

**R22** M.Tech.

YEAR

₽Ġ ₽ROGRAMME

In case the candidate is placed in 'l' grade, he/she has to appear for both Phase-I and Phase-II assessments, which will be held within the 15 days after declaration of results. In the consecutive assessment also if the candidate fails to secure min. required score, then he / she will be placed in 'R' grade.

### 5.8 Internship

Internship work is undertaken by a student in an industry, under the joint supervision of industry personnel and an internal faculty member. Sixty percentage of the marks of Internship are allotted through continuous evaluation as formative assessment and the remaining 40% are based on summative assessment.

Table 7: Assessment scheme for Internship reviews.

| Semester     | Module     | Schedule         | Review        | Formative<br>assessment marks |

|--------------|------------|------------------|---------------|-------------------------------|

| Semester III | Module -1  | 7th – 8th Week   | First review  | 20                            |

| Semester III | Module - 2 | 15th – 16th Week | Second review | 40                            |

| Somester IV  | Module - 1 | 7th – 8th Week   | First review  | 20                            |

| Semester IV  | Module - 2 | 15th – 16th Week | Second review | 40                            |

- a) The progress of internship work is reviewed twice in every semester by the "Internship Review- Committee (IRC)" and marks for formative assessment are awarded based on these reviews.

- b) The IRC consists of Head of Department or his/her nominee (Chairperson), the internal and external (industry) supervisors.

- c) The IRC may not be the same for all students; however, the same IRC should exist for entire duration of the internship program of any single student.

- d) The schedule and the scheme of evaluation are to be announced with internship notification. The internship reviews may take place at the place of internship or at the university, as decided by the interning organization or may be conducted in the blended mode.

### 5.8.1 Formative assessment: Internal reviews at the place of internship

The internal supervisor will interact with the guide allotted at internship offering industry based on the schedule given to conduct the reviews. Scheduled reviews can be conducted by IRC on online mode for discussion/ presentation. The marks shall be distributed for each student in the scheduled reviews as given in Table (7).

- a) Students should submit a report (not more than two pages) explaining about the progress of their work, mentioning clearly details like the machines or software handled / adopted, type of data collected and his/her understanding and contribution in the programme, and the same has to be presented before the supervisors.

- b) The candidate should clearly present the completion of stipulated assignments set by the industry supervisor for that period.

- c) The evaluation will be based on a & b above and also based on regularity and discipline maintained in the internship venue.

Table 8: Suggested scheme of assessment for every review

| Component                                            | First review | Second review |

|------------------------------------------------------|--------------|---------------|

| Regularity and interaction                           | 5            | 10            |

| Application of knowledge                             | 3            | 6             |

| Gaining of new knowledge /skills / literature survey | 3            | 6             |

| Internship progress                                  | 5            | 10            |

| Report                                               | 4            | 8             |

| Total marks                                          | 20           | 40            |

### 5.8.2 Summative assessment – Internship

At the end of III and IV semesters, the student shall submit a comprehensive report of internship covering the work done and make a final presentation in two phases as follows:

Phase–I: A committee of two members comprising of internal supervisor and HoD's nominee will assess the overall internship participation by the candidate and his final report through presentation made by the intern. The internship report (6 marks), presentation (7 marks) and overall impression (7 marks) during the internship will be evaluated respectively.

Phase–II: A final presentation and defense assessment for a max. of 20 marks will be carried out by one-man committee composed of an external expert who is chosen by the Dean AAA from a panel of examiners suggested by the HoD. The format for evaluation will involve going through the project report's quality (6 marks), presentation (6 marks) and interaction and defense (8 marks).

The qualifying marks will be finalized considering the marks scored in both the phases (I & II) of summative assessment.

Publication in a top-notch conference / peer-reviewed journal is mandatory for evaluating the Internship for 100% weightage.

In case the candidate is placed in 'I' grade, he / she has to appear for both Phase-I and Phase-II assessments, which will be held within the 15 days after declaration of results. In the consecutive assessment also if the candidate fails to secure min. required score, then he / she will be placed in 'R' grade.

### 6. SEMESTER-END ASSESSMENT ACTIVITIES

- 6.1 Setting of semester-end summative assessment question papers will be coordinated by the instructor assigned for a particular course. Two sets of question papers will be submitted latest by 12th week of the semester.

- 6.2 There shall be 'Summative Assessment Question Paper Scrutiny Committee' which would be constituted with external experts. Experts are empowered to modify / rephrase the questions to maintain a high standard of the semester-end assessment. The review should be completed by the 14th week of the semester. The review process will be coordinated by a committee of School Dean, HoDs and external experts.

- 6.3 The question wise marks scored in the summative assessment out of a total of 80 will be made available online within two weeks from the last date of examination and would be kept active for 24 hours. Latest by the end of 48 hours from the instant of notification any candidate can submit an appeal online providing question wise claim.

- 6.4 Claims for re-assessment on P-based courses are not allowed.

- 6.5 The appeals will be attended within next three working days. Fees for appeal, as decided from time to time, has to be remitted online along with the appeal.

- 6.6 Final results and grades will be computed as explained in the next section.

- 6.7 Final results and grades shall be announced within four weeks of completion of the last examination of the summative assessment (within two weeks from the last date of appeal). Grades are published on the University website, and also informed to the parents and students through SMS.

- 6.8 Provisional Grade cards will be issued within two weeks after the announcement of grades. Grade card will contain three parts. Part 1: Details of successfully completed courses. Part 2: Details of 'l' grade courses. Part 3: Details of 'R' grade courses.

### 7 COMPUTATION OF GRADING

7.1 Formative assessment decides the list of 'R'- candidates. Therefore, these candidates will not be considered for grading computation. Summative assessments decide the list of 'l' candidates. Therefore, these candidates will not be considered for grading computation.

- 7.2 The candidates who have successfully completed both formative and summative assessments will be considered for computation of relative grading.

- 7.3 Threshold value (**Th**) for relative grading in each course is arrived after studying the marks distribution in that course by a committee constituted by office of Dean AAA. The threshold value is decided by the upper bound marks of the major chunk of the class keeping the top outlier scores away from consideration (the least upper bound). The threshold value will be slightly greater than upper bound marks or may be equal to the upper bound marks.

- 7.4 The total marks (m) = marks scored in the formative assessment + marks scored in the summative assessment is transformed into relative grade expressed accurate to two decimal places as follows:

### Relative grade point (P) = (m/Th) X 10 [and limited to 10]

7.5 If students require course wise percentage equivalence, then the calculation will be based on the following

### Course wise percentage equivalence = (m/Th) X100 [truncated to two-digit integer and limited to 100]

7.6 After relative grading, a student is assigned a 'Letter Grade (G)' for each course as per Table (9). The grade and the corresponding letter grade represent the outcomes and assessments of a student's performance in a course.

### Table 9: Grading information

| Relative Grading Range (P) | Category    | Grade (G) |

|----------------------------|-------------|-----------|

| ≥ 9.50                     | Outstanding | 0         |

| ≥ 8.50 to 9.49             | Excellent   | S         |

| ≥ 7.00 to 8.49             | Very good   | A         |

| ≥ 6.00 to 6.99             | Good        | В         |

| ≥ 5.00 to 5.99             | Fair        | С         |

| ≥ 4.50 to 4.99             | Marginal    | М         |

| Transitional Grade         | Repeat      | R         |

| Transitional Grade         | Incomplete  | I         |

### 8. SUPPLEMENTARY EXAMINATIONS

- 8.1 The supplementary examinations shall be conducted once in summer semester. Notifications will be released by the AAA section informing the students about registration procedures, details of fee and timetables. Apart from these examinations the students who have courses with 'l'-grade can also write the supplementary examinations along with regular semester-end examinations of that academic (Odd / Even) semester.

- 8.2 Whenever a candidate clears courses with 'l' grade in a supplementary examination that are conducted during a regular semester, the Threshold value for computing his / her grade will be obtained from the same batch in which he / she had completed his / her formative assessment.

- 8.3 Whenever a candidate clears courses with 'R' / 'I' grade in a summer semester, the Threshold value for computing his / her grade will be carry forwarded from the preceding Odd / Even semester for the respective courses.

- 8.4 Whenever a candidate clears courses with a 'R' grade in a regular semester along with his/ her junior batch then for this candidate the Threshold value will be corresponding to his/her junior batch for computing grade.

- 8.5 The results of summative assessment of Project / Internship will be announced only if the candidate successfully earn all the credits in courses registered during the program. If the candidate is with 'R' / 'I' graded courses the results will be kept under 'Announced Later (L)' status and will be announced only after candidate clears these courses.

### 9. GRADE POINT AVERAGE

The Academic Performance of a student in every semester is indicated by the Semester Grade Point Average (SGPA) and finally by Cumulative Grade Point Average (CGPA).

### 9.1 SGPA

The Semester Grade Point Average (SGPA) shall be computed using the formula given below:

$$SGPA = \frac{\sum_{i=1}^{n} C_i P_i}{\sum_{i=1}^{n} C_i}$$

Where

n = number of courses a student successfully completed in the semester under consideration

Pi = Grade points secured for the i<sup>th</sup> course registered in the semester under consideration.

Ci = the number of credits assigned to i<sup>th</sup> course registered in the semester under consideration.

### 9.2 CGPA

The Cumulative Grade Point Average (CGPA) shall be computed after successful completion of the programme. The CGPA shall be expressed in different flavors to reflect M.Tech. of 68 credits, and Add-on certification up to 12 credits.

Accordingly, the computations will be as below:

$$CGPA = \frac{\sum_{j=1}^{m} C_j P_j}{\sum_{j=1}^{m} C_j}$$

Where

m = total number of courses prescribed for the completion of the programme

Pj = grade points secured for the j<sup>th</sup> course.

Cj = the number of credits assigned to j<sup>th</sup> course

and  $\Sigma C_j = 68$

$\Sigma$  Cj = 08 for CGPA calculations in case of M.Tech. with Add-on certification